🧩 1. Why Look Inside RAM?

So far, we’ve talked about what RAM does – fast memory, short-term workspace, random access. But how is it actually constructed?

To truly understand RAM, we need to zoom in:

-

From the chip you plug into your computer 💻

-

To the circuits inside ⚡

-

To the tiny cells that hold individual 1s and 0s

Think of this as going from the outside of a house (the RAM stick) to the rooms and bricks inside (the cells and circuits).

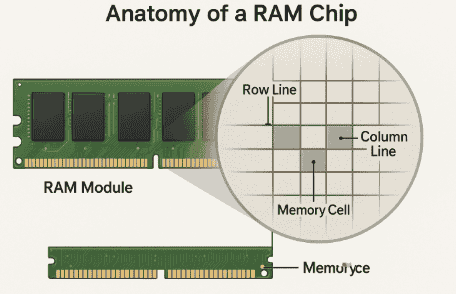

2. What Does a RAM Chip Look Like?

When you buy a RAM module (also called a DIMM – Dual Inline Memory Module), it looks like:

-

A green or black circuit board (the “stick”)

-

With several small black rectangles on it (the memory chips)

Each black chip contains millions or billions of memory cells, where data is stored temporarily.

👉 So the RAM stick you insert into your motherboard is actually just a holder for multiple RAM chips, which themselves hold billions of bits.

3. Memory Cells – The Smallest Building Blocks

The fundamental unit of RAM is the memory cell.

-

Each cell holds 1 bit (either 0 or 1).

-

A bit is stored as an electrical charge (in DRAM) or as a flip-flop state (in SRAM).

Two major types of cells:

-

DRAM (Dynamic RAM) → Uses a capacitor + transistor.

-

Capacitor = tiny bucket that can either hold charge (1) or be empty (0).

-

Transistor = tiny switch that controls access to the capacitor.

-

Needs to be refreshed constantly (capacitors leak charge).

-

-

SRAM (Static RAM) → Uses 6 transistors arranged in a flip-flop.

-

Holds data as long as power is on.

-

Faster but takes more space, so more expensive.

-

👉 That’s why your main computer memory is DRAM, while caches inside the CPU use SRAM.

4. Organizing the Cells – Rows and Columns

Billions of memory cells can’t just sit randomly scattered. They need to be organized.

RAM cells are arranged in a grid, like a spreadsheet:

-

Rows → Large groups of cells connected together.

-

Columns → The vertical access points.

To access a single bit, the CPU doesn’t go cell by cell. Instead, it uses:

-

Row Address → Which row to open

-

Column Address → Which column to select within that row

This system is called RAS (Row Address Strobe) and CAS (Column Address Strobe).

-

The memory controller sends signals to activate a row, then pick the right column.

-

The bit value is then read out or written in.

5. Memory Banks – Dividing the Work

A RAM chip isn’t just one giant grid—it’s split into banks.

-

Each bank can work independently.

-

While one bank is refreshing, another can be accessed.

-

This allows RAM to handle multiple requests in parallel, speeding things up.

Think of it like a library with many rooms (banks). While one room is being cleaned, students can still read in another.

6. Hierarchy Inside RAM

Inside each RAM chip:

-

Cells are grouped into rows and columns.

-

Rows/columns are grouped into banks.

-

Banks together form the chip.

-

Multiple chips sit on one module (DIMM).

So the hierarchy looks like this:

Bit → Cell → Row/Column → Bank → Chip → Module

This layered structure is why RAM can serve billions of bits so quickly—it’s carefully organized.

7. The Role of the Memory Controller

How does the CPU actually talk to RAM?

Enter the memory controller.

-

A special circuit that translates CPU requests into row and column addresses.

-

Controls the timing of when rows open, when data is read/written, and when cells are refreshed.

-

In modern computers, the memory controller is built directly into the CPU itself.

Without the controller, RAM would just be a pile of cells with no way to manage them.

8. Refresh Cycles – Keeping Data Alive

One of the unique quirks of DRAM is that capacitors leak charge.

-

After a few milliseconds, a “1” may drain into a “0”.

-

To prevent this, RAM must refresh all cells thousands of times per second.

This means the memory controller is constantly:

-

Reading a row

-

Rewriting it back before it fades

You don’t notice this because it happens in nanoseconds, but it’s a crucial reason why DRAM is called dynamic.

9. How a Single Bit is Read (Step by Step)

Let’s walk through an example:

-

CPU says: “Give me the data at address 00101011.”

-

Memory controller splits it into:

-

Row: 0010

-

Column: 1011

-

-

Row 0010 is activated.

-

Column 1011 is selected.

-

The capacitor in that cell is checked:

-

If charged → 1

-

If empty → 0

-

-

Value is sent back to the CPU.

This happens in nanoseconds—millions of times faster than you can blink.

10. Why This Structure Matters for Performance

The row/column/bank system explains why:

-

More banks → Better parallelism (parallelism means multiple things can be done at the same time, in parallel) → Faster performance

-

Wider modules (more chips) → More data can move at once

-

Timing delays (CAS latency) → Depend on how quickly rows/columns open

So when you see RAM specifications like DDR4-3200 CL16, those numbers come directly from this internal structure.

11. Recap of Key Ideas

-

A memory cell stores a single bit (0 or 1).

-

Cells are arranged in rows and columns.

-

Groups of rows/columns = banks.

-

Banks form a chip, and multiple chips form a RAM module.

-

The memory controller manages addressing, timing, and refresh cycles.

-

DRAM must be refreshed constantly because capacitors leak charge.